# **Introduction of Fast Electronics**

#### RYU, Min Sang University of Seoul

SPDAK 2021 in KNU

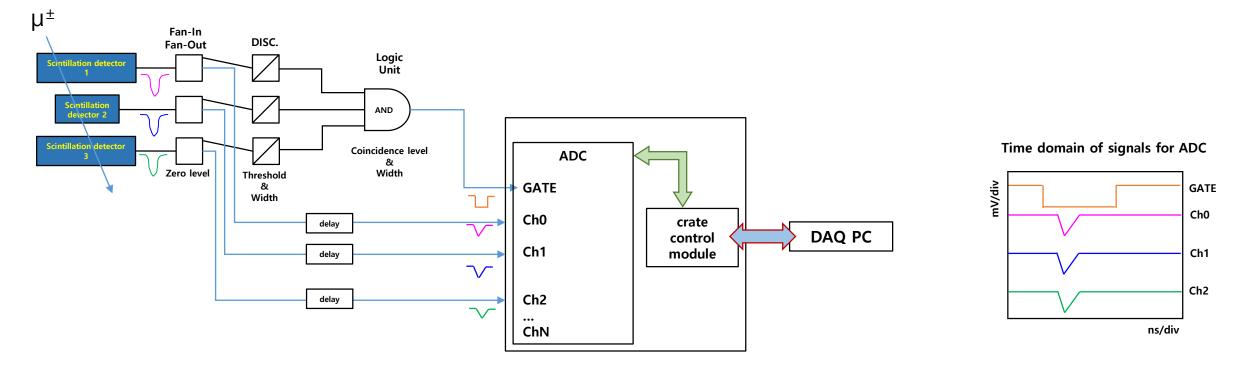

- Role of DAQ in HEP experiment

- Readout scheme for DAQ

- ♦ Fast electronics

- Signal and Device impedance

- Preamplifier

- Fan-In and Fan-Out

- Discriminator (LED & CFD)

- Logic Unit for coincidence

- TDC & ADC

- Summary

#### 2021. Jan. 22

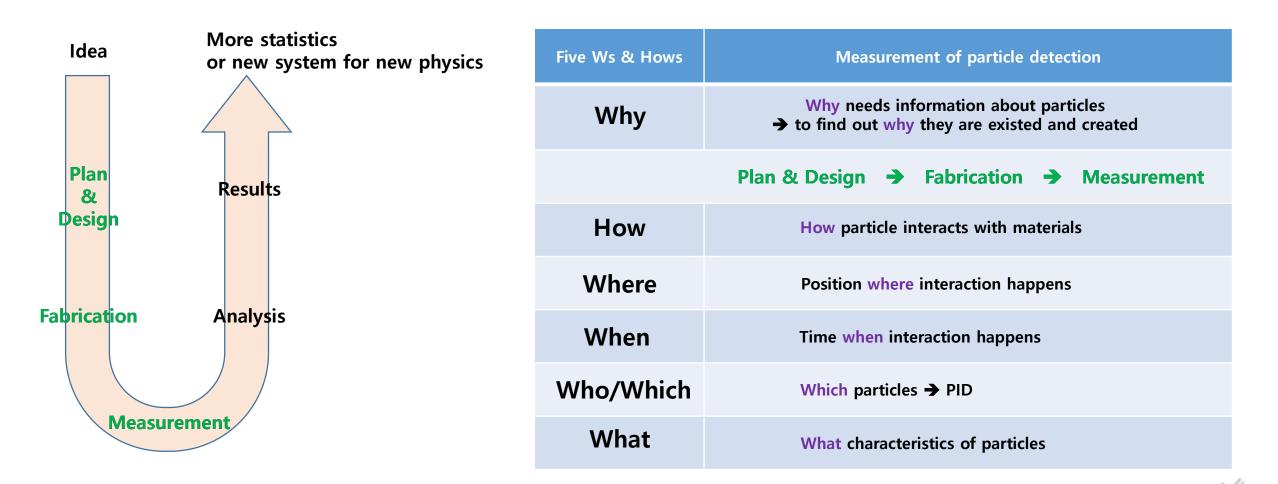

#### **Role of DAQ System in HEP experiment**

How do we watch an event in HEP experiments?

We design, fabricate, test, and use the readout system (or fast electronics) for data acquisition (DAQ)

#### Readout scheme for data acquisition (DAQ)

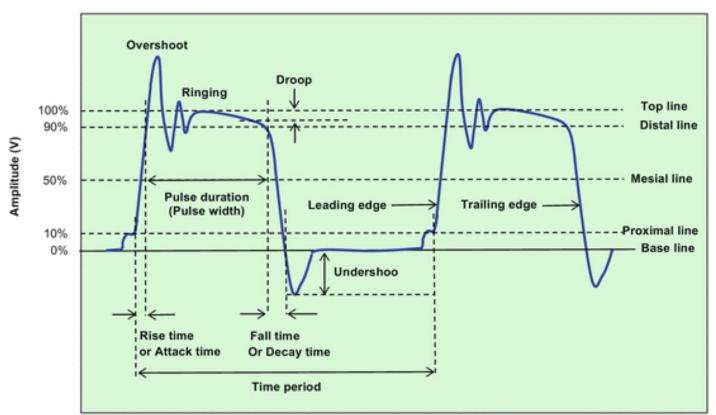

#### **Components of waveform**

Base line Pulse height Pulse width

Proximal line: 10% of pulse heightMesial line: 50% of pulse heightDistal line: 90% of pulse height

Rise time (or attack time) at leading edge

Fall time (or decay time) at trailing edge

→ These depend on the polarity of waveform.

Overshoot Undershoot Ringing

Time period

#### https://link.springer.com/chapter/10.1007/978-3-319-25448-7\_7

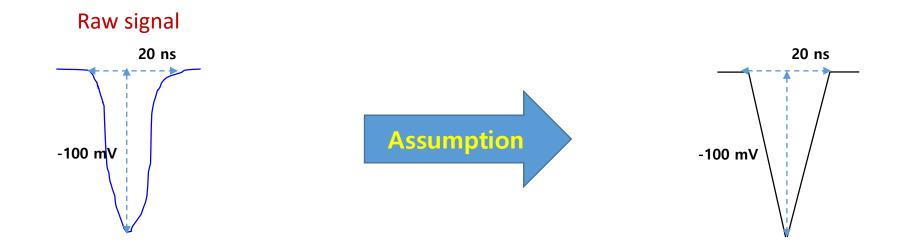

### Charge of raw signal

Electric charge of analog signal with assumption:

$$Q(C) = \frac{V(V) \cdot t(s)}{2 \cdot R(\Omega)} = \frac{-0.1 V \cdot 20 ns}{2 \cdot 50\Omega} = -20 pC$$

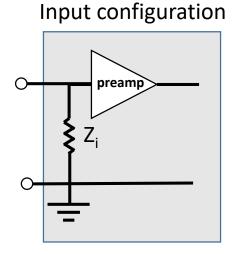

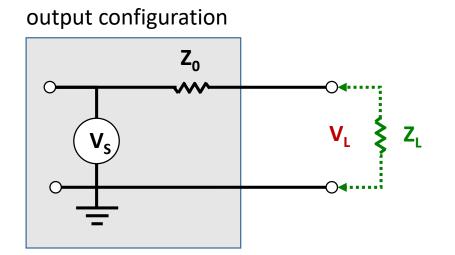

## **Device impedances**

A basic concept in the processing of pulses from radiation detectors is the impedance of the devices that comprise the signal-processing chain.

Voltage ( $V_L$ ) appearing across a loading ( $Z_L$ ) by voltage-divider relation

$$V_L = V_S \frac{Z_L}{Z_0 + Z_L}$$

For the open-circuit or unloaded  $(Z_L = \infty)$ , voltage is  $V_L = V_S$ .  $\rightarrow$  not for the real experiment

To preserve maximum signal level, one normally wants  $V_L$  to be as large a fraction of  $V_S$  as possible. For  $Z_L \gg Z_0$  then  $V_L \cong V_S \rightarrow$  Fan-In & Fan-Out, Discriminator, ADC, etc

For  $Z_L = Z_0$  then  $V_L = V_S/2$   $\rightarrow$  Divider or Splitter

#### Preamplifier

| Role     | converting a raw signal from the detector into output signal with gain      |

|----------|-----------------------------------------------------------------------------|

| Location | placing close to the detector to reduce the noise and avoid the signal loss |

#### $\checkmark$ Specification for design

- Dynamic range

- Size of input signal

- Pulse pileup

- Signal-to-noise ratio

- Power consumption

#### $\checkmark$ Configuration

- Voltage-sensitive preamplifiers

- Current-sensitive preamplifiers

- Charge-sensitive preamplifiers

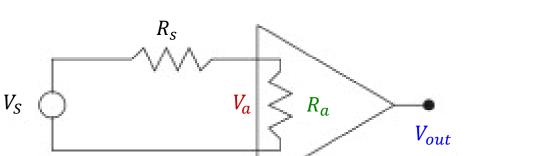

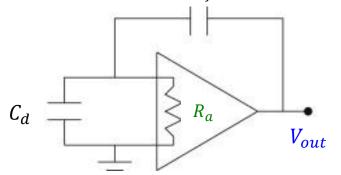

## **Voltage-sensitive preamplifiers**

Design principle of V-sensitive preamp

Simplified realistic V-sensitive preamp

Signal voltage  $V_S$ Voltage at the input stage of the amplifier  $V_a$ Output voltage  $V_{out}$

$$V_a = V_S \frac{R_a}{R_s + R_a}$$

Any current drawn would decrease the potential drop across  $R_{s.}$  Ideally, its input resistance have to be infinite. But it can only be achieved up to a good approximation.

For  $R_a \gg R_S$  then  $V_a \cong V_S$ then  $V_{out} = Gain \times V_a \approx Gain \times V_S$

Signal voltage  $V_S = Q/C_d$

Q: collected charge on the readout electrode ( $Q = \int_0^{t_0} i_s(t) dt$ ) C<sub>d</sub>: combined detector and stray capacitance

then

$$V_{out} \approx Gain \times \frac{Q}{C_d} = \frac{Gain}{C_d} \int_0^{t_0} i_s(t) dt$$

Since we are integrating the current to convert it into voltage,  $C_d$  should discharge slower than the charge collection time  $t_d << R_aC_d$ .

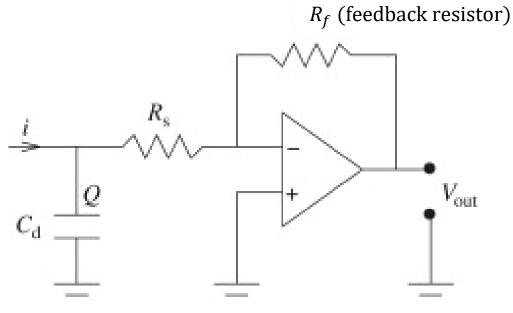

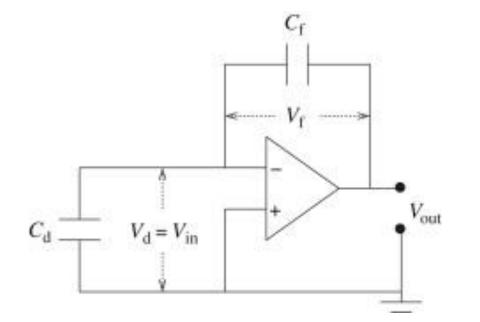

### **Charge-sensitive preamplifiers**

*C<sub>f</sub>* (feedback capacitance)

Basic principle of Q-sensitive preamp

The dependence of a voltage-sensitive preamplifier on the input capacitance is a serious problem for many detection systems. → to develop Q-sensitive preamplifiers

The charge  $(Q_d)$  accumulated on the electrode  $(C_d)$  is integrated on another capacitor  $(C_f)$ . Then the potential  $(V_f)$  on that capacitor is then directly proportional to the original charge  $(Q_d)$  on the detector.

$$V_{out} \propto \frac{Q_f}{C_f} \propto \frac{Q_d}{C_f}$$

The condition that  $Q_f \approx Q_d$  can only be achieved if no current flows into the preamplifier's input with  $R_a \rightarrow \infty$ .

Simple Q-sensitive preamp

#### **Preamplifiers**

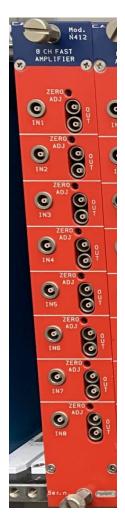

#### **CAEN N412 8ch Fast Amplifier**

#### INPUTS:

50Ω impedance.

Reflection coefficient: ≤ 6% over input dynamic range.

- Quiescent voltage: < ± 5 mV.

#### OUTPUTS:

Risetime: ≤ 3.0 ns.

- Falltime: ≤ 2.0 ns.

- Maximum positive amplitude (linear): 400 mV (50Ω impedance).

Maximum negative amplitude (linear): -4 V (50Ω impedance).

- Overshoot: ± 10% for input risetimes of 2 ns and with the 2nd output terminated in 50Ω.

- Quiescent voltage adjustable (via front panel trimmer for each channel) in the range from -20 mV to +50 mV.

#### GENERAL:

Gain: fixed 10 ± 3%, non-inverting

- Coupling: direct.

I/O delay: ≤ 12 ns.

- Noise: less than 1 mV, referred to input.

Interchannel crosstalk: better than -56 dB in the worst test condition, and with both the outputs of the tested channel terminated in 50Ω.

Bandwidth:

160 MHz (with both the channel's outputs terminated in 50Ω);

180 MHz (single ended output).

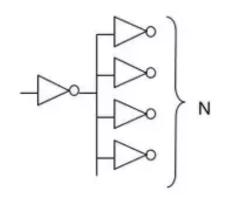

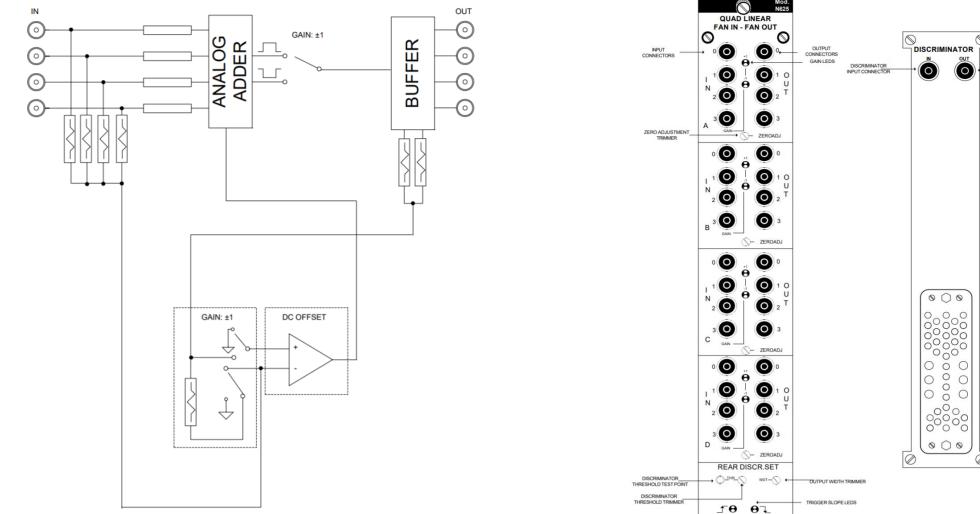

## Fan-In and Fan-Out (FIFO)

Fan-in: maximum number of input signals feeding into the input of a logic system

Fan-out: maximum number of output signals from the output of a logic system

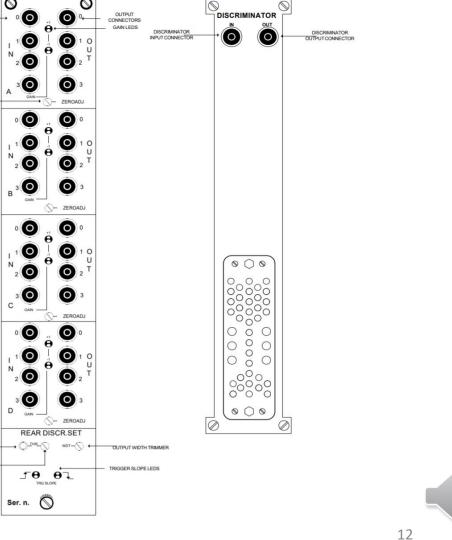

### Fan-In and Fan-Out (FIFO)

CAEN N625 Quad Linear Fan In / Fan Out

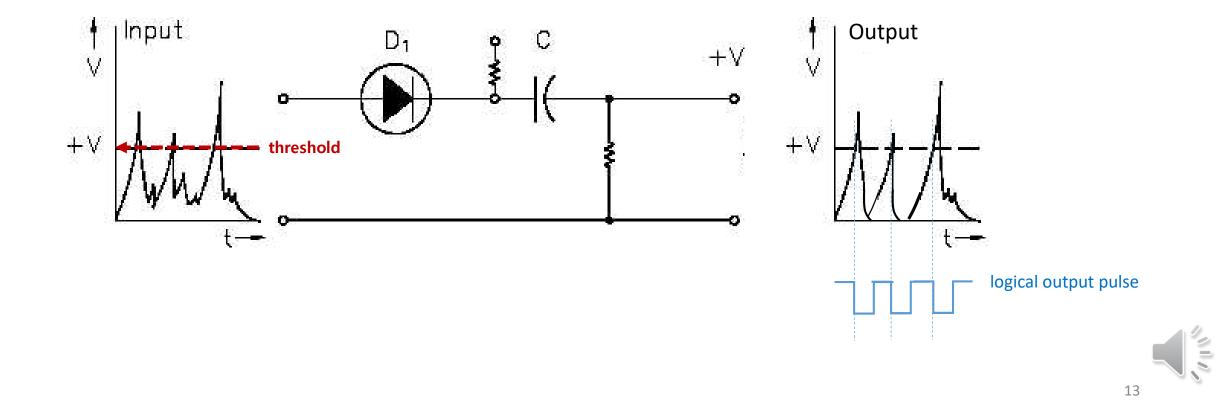

# **Discriminator (DISC)**

Role: generating the logical output pulse when the input pulse exceeds the discriminator preset level

→ If input voltages exceeds the threshold value +V then diode  $D_1$  conducts and DISC generates the logical output pulses.

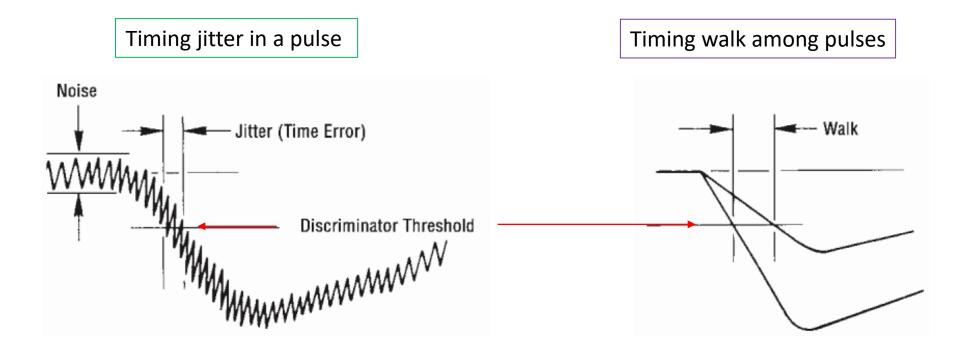

## Timing jitter and walk

The contribution of noise to the (Timing) Jitter

Timing Jitter =  $e_{noise}/(dV/dt)$

**e**<sub>noise</sub>: voltage amplitude of the noise superimposed on the analog pulse

**dV/dt:** slope of the signal when its leading edge crosses the discriminator threshold

"(Timing) Walk" is the systematic dependence of the time marker on the amplitude of the input pulse.

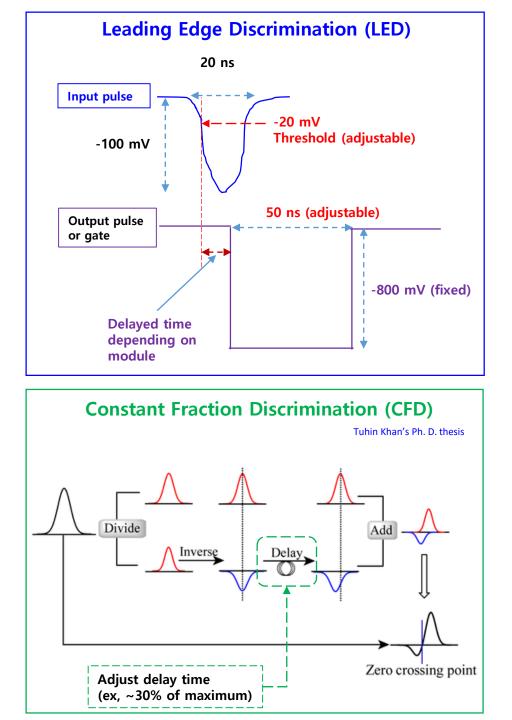

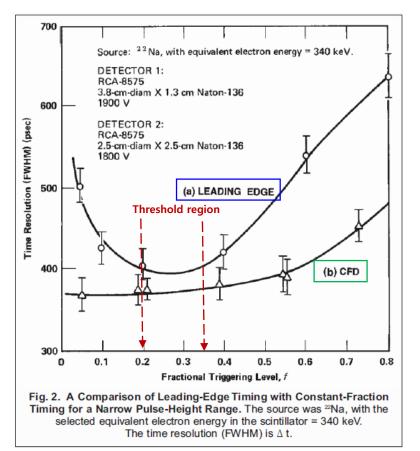

#### **LED** and **CFD**

http://www.peo-radiation-technology.com/wp-content/uploads/2015/09/ort\_15\_fast-timing-discriminators\_datasheet\_peo.pdf

Time resolution:  $\sigma_{CFD} < \sigma_{LED}$

#### https://www.wekipedia.com

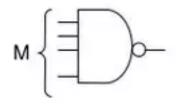

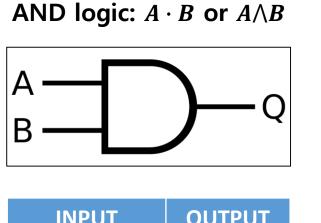

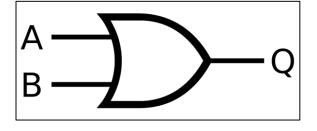

### **Role of Logic Unit**

Role: generating the gating pulse when the preset of logical algorism against with inputs is true

| INF | TUY | OUTPUT |

|-----|-----|--------|

| А   | В   | Q      |

| 0   | 0   | 0      |

| 0   | 1   | 0      |

| 1   | 0   | 0      |

| 1   | 1   | 1      |

OR logic: A + B or  $A \vee B$

| INF | TUT | OUTPUT |

|-----|-----|--------|

| А   | В   | Q      |

| 0   | 0   | 0      |

| 0   | 1   | 1      |

| 1   | 0   | 1      |

| 1   | 1   | 1      |

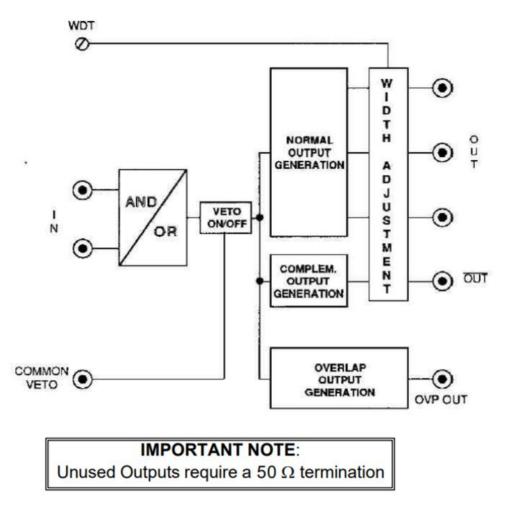

# Logic Unit

UAD COINCIDENCE LOGIC UNIT Mod. N455 AND WDT VP OU AND VP OUT AND OUT WDT VP OU AND OR

https://www.caen.it

**CAEN N455 Quad Coincidence Logic Unit**

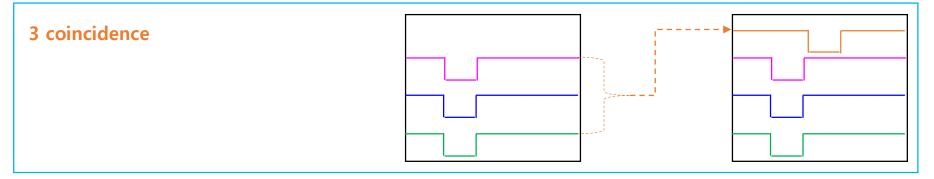

#### **Coincidence** with 3 inputs

When events occur, the input signals from many detectors can be matched with Logic Unit.

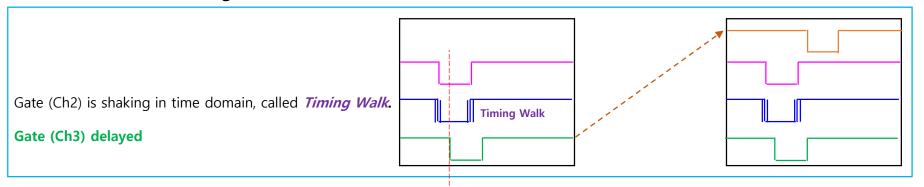

#### Coincidence with timing walk

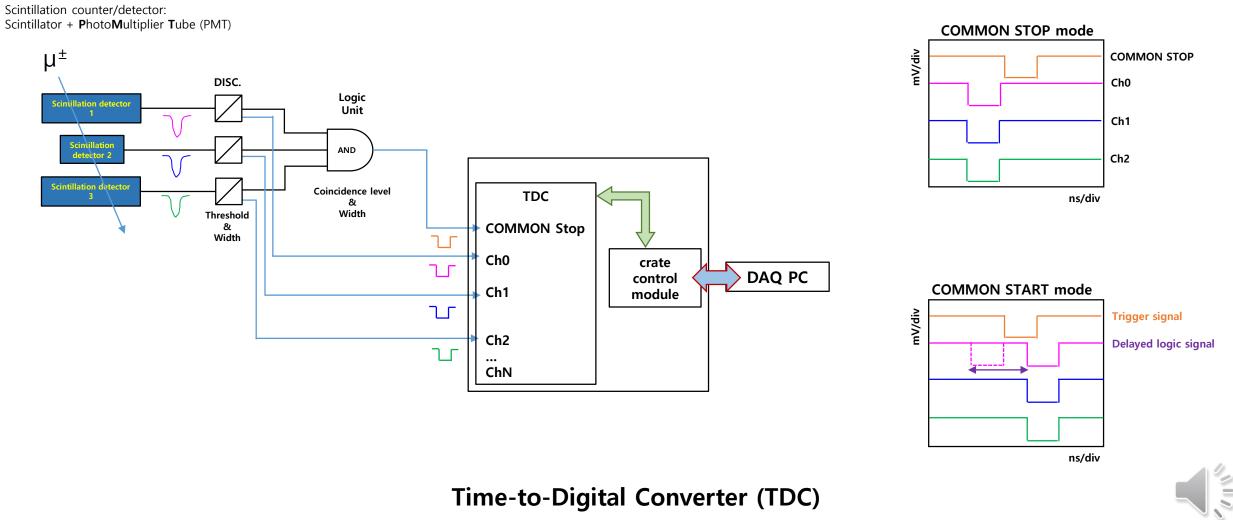

#### Time measurements with TDC

**Operation mode of TDC: COMMON STOP/START?**

#### How to record time in TDC?

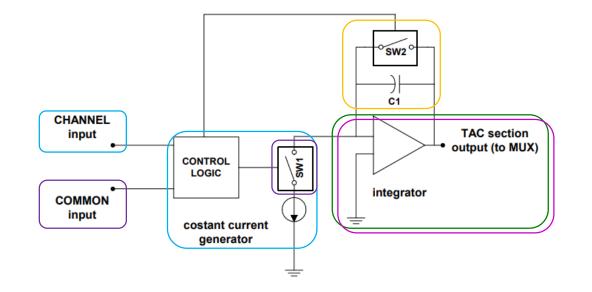

Block diagram of TAC section in CAEN V775N 16ch MultiEvent TDCs

A Start signal closes the **switch SW1** thus allowing a constant current to flow through an integrator; a Stop signal opens the **switch SW1** again.

The constant current generates a **linear ramp voltage which is stopped at an amplitude proportional to the time interval** between Start and Stop pulses.

After digitization the **SW2 switch** is closed by the CLEAR signal which allows the discharge of the **capacitor C1**.

Both the COMMON and CLEAR signals are controlled by the CONTROL LOGIC section.

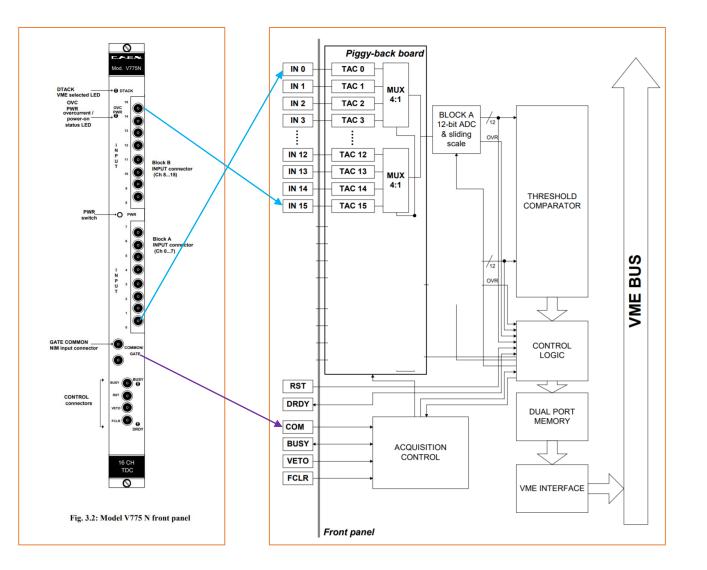

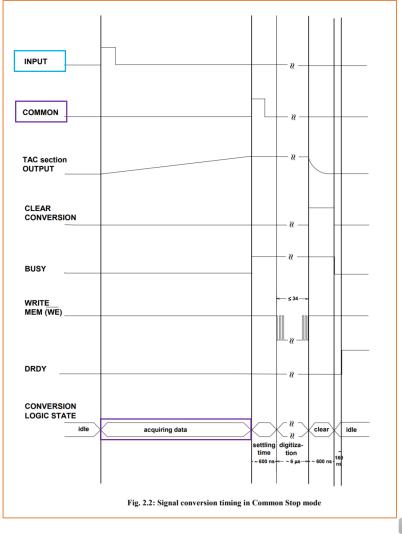

### TDC and signal conversion timing

CAEN V775N 16ch MultiEvent TDCs

21

#### Charge measurements with ADC

Scintillation counter/detector: Scintillator + **P**hoto**M**ultiplier **T**ube (PMT)

#### How to record charge in ADC?

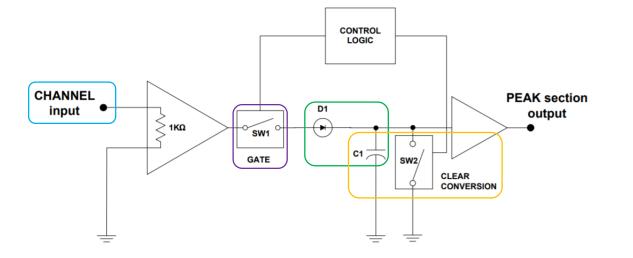

Block diagram of PEAK section in CAEN V1785 8ch Dual Range Peak ADC

#### COMMON STOP mode

The **GATE signal** closes the **switch SW1** thus allowing the **capacitor C1** to be charged as the **diode D1** is forward-biased by the signal.

As the SW1 is open again, the signal is digitized by the 12-bit ADCs.

After digitization the SW2 switch is closed by the CLEAR signal which allows the discharge of the capacitor C1.

Both the GATE and CLEAR signals are controlled by the CONTROL LOGIC section.

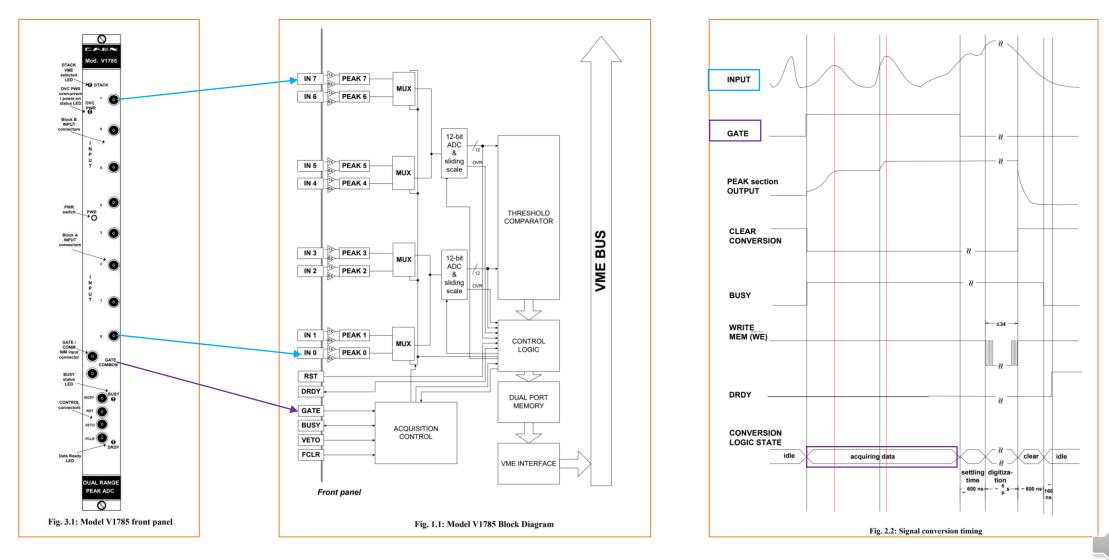

### ADC and signal conversion timing

CAEN V1785 8ch Dual Range Peak ADC

Dual input range:  $0 \div 4 \text{ V} / 0 \div 500 \text{ mV}$ Gain: 1 mV/count and 125 uV/count for High and Low ranges

24

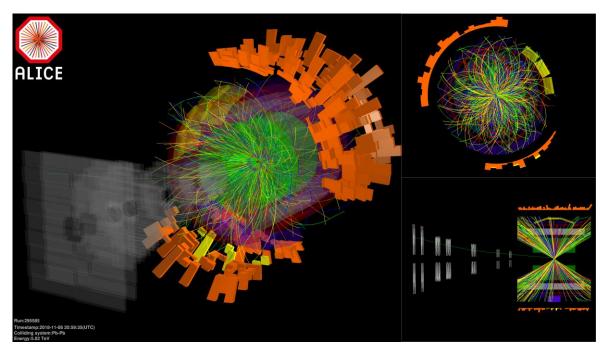

#### Summary: Event in HEP experiment

**"Fast Electronics"** are a main component of particle detection system to see what happens in the HEP experiments.

First Pb collision of ALICE experiment at  $\sqrt{s}$  = 5.02 TeV in 2018 https://cds.cern.ch/record/2646381

# Thank you

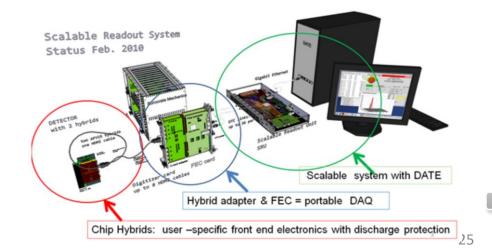

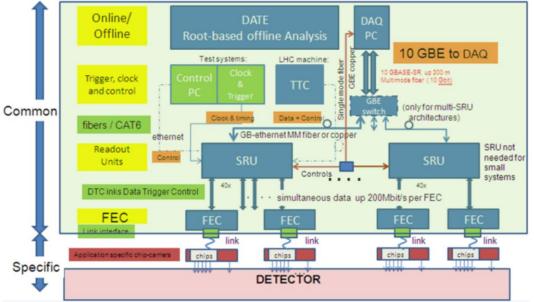

#### RD51 Scalable Readout System (SRS)

https://indico.cern.ch/event/77597/contributions/2088463/attachments/1056845/1506857/RD51-SRS-Description.pdf

physical overview SRS of RD51